# Propelling SAT-based Debugging using Reverse Domination

Bao Le, Hratch Mangassarian, Brian Keng, Andreas Veneris

University of Toronto

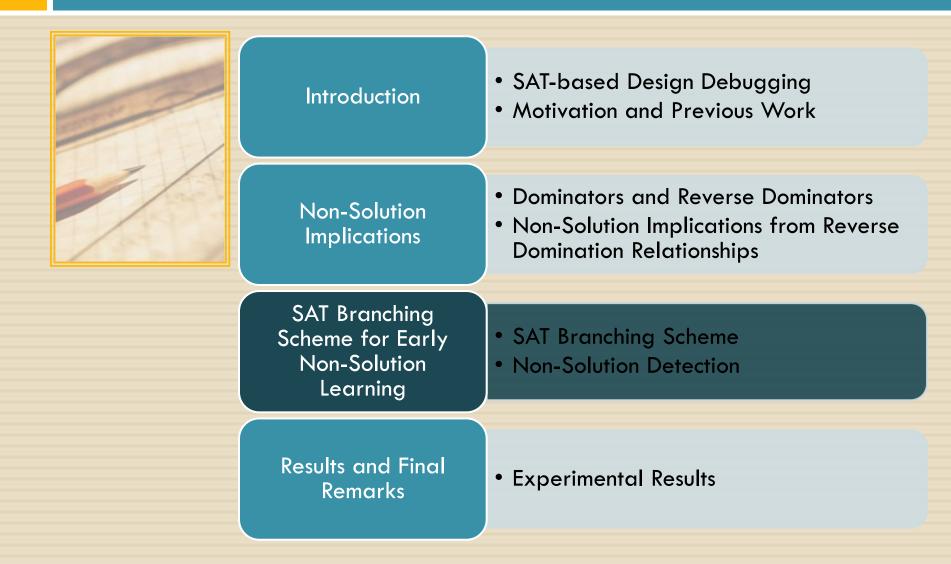

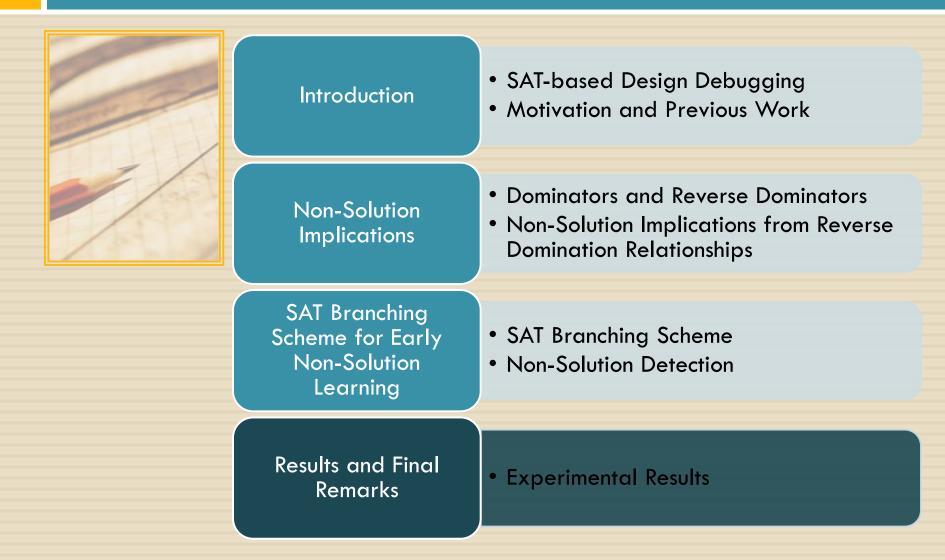

| Introduction                                                  | <ul><li>SAT-based Design Debugging</li><li>Motivation and Previous Work</li></ul>                                                  |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Non-Solution<br>Implications                                  | <ul> <li>Dominators and Reverse Dominators</li> <li>Non-Solution Implications from Reverse<br/>Domination Relationships</li> </ul> |

| SAT Branching<br>Scheme for Early<br>Non-Solution<br>Learning | <ul><li>SAT Branching Scheme</li><li>Non-Solution Detection</li></ul>                                                              |

| Results and Final<br>Remarks                                  | • Experimental Results                                                                                                             |

| Introduction                                                  | <ul><li>SAT-based Design Debugging</li><li>Domination Relationships</li></ul>                                                      |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Non-Solution<br>Implications                                  | <ul> <li>Dominators and Reverse Dominators</li> <li>Non-Solution Implications from Reverse<br/>Domination Relationships</li> </ul> |

| SAT Branching<br>Scheme for Early<br>Non-Solution<br>Learning | <ul><li>SAT Branching Scheme</li><li>Non-Solution Detection</li></ul>                                                              |

| Results and Final<br>Remarks                                  | • Experimental Results                                                                                                             |

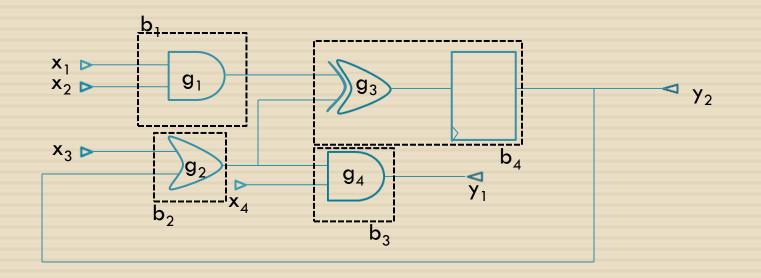

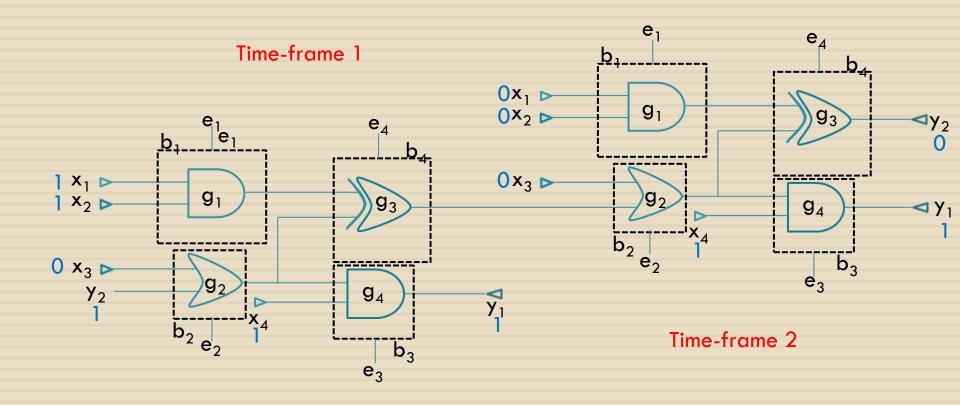

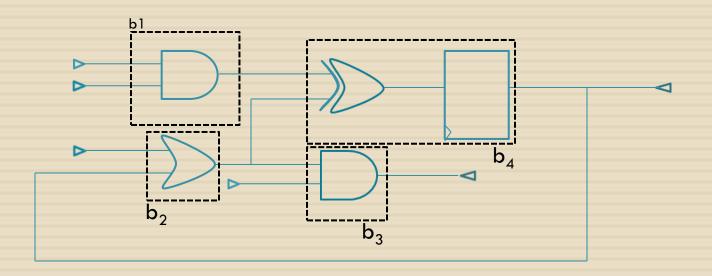

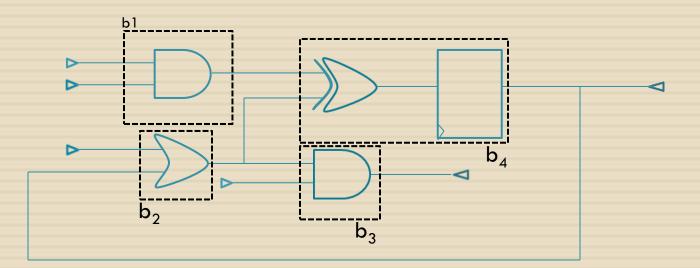

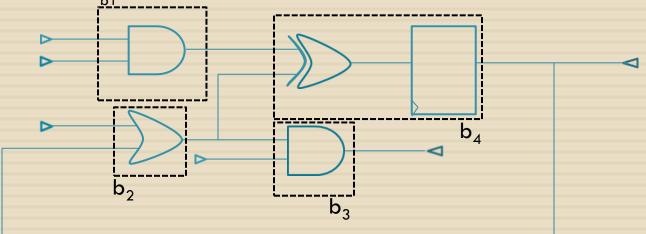

Given an erroneous circuit, a counter example of length k, and error cardinality N:

- Goal: Return shortlist of potentially buggy RTL blocks (solutions)

- Blocks that can be modified to fix counter-example

- Procedure:

- An error-select variable  $e_i$  is inserted at the outputs of each RTL block.

- $e_i = 1$  disconnects block from fan-ins, making its outputs free variables

- $e_i = 0$  does not modify the circuit

- **\square** Enhanced circuit is replicated k times using time-frame expansion.

- Initial state, primary inputs and outputs are constrained to expected behavior of counter-example.

- Each satisfying assignment to  $e = \{e_1, \dots, e_n\}$  is a debugging solution

- The SAT solver must find all such assignments to e using blocking clauses.

#### Example:

SAT Solver returns  $e_4 = 1$  for N = 1; therefore, block  $b_4$  (i.e. gate  $g_3$ ) is the bug.

#### SAT-based Design Debugging

- Fault diagnosis and logic debugging using Boolean Satisfiability [Smith, Veneris, Ali, Viglas-TCAD2005]

- Large designs, long counter-examples pose a scalability challenge even to modern SAT solvers.

#### Our contributions:

- On-the-fly discovery of implied non-solution blocks using reverse domination

- Goal is to prune the search space of design debugging

1.7x speed up in SAT solving time.

| Introduction                                                  | <ul><li>SAT-based Design Debugging</li><li>Motivation and Previous Work</li></ul>                                                  |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Non-Solution<br>Implications                                  | <ul> <li>Dominators and Reverse Dominators</li> <li>Non-Solution Implications from Reverse<br/>Domination Relationships</li> </ul> |

| SAT Branching<br>Scheme for Early<br>Non-Solution<br>Learning | <ul><li>SAT Branching Scheme</li><li>Non-Solution Detection</li></ul>                                                              |

| Results and Final<br>Remarks                                  | • Experimental Results                                                                                                             |

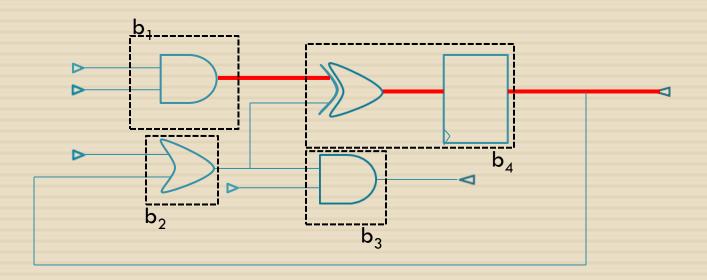

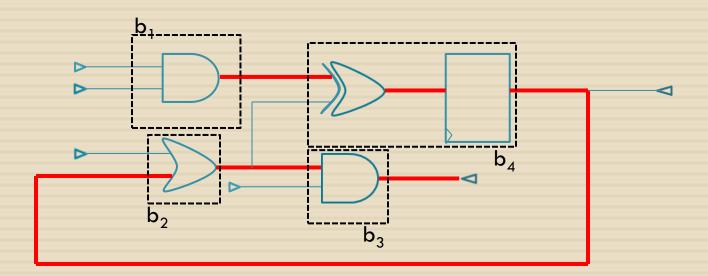

Block  $b_j$  is said to dominate block  $b_i$  if any path from a node in  $b_i$  to a primary output passes through a node in  $b_j$ .

Block  $b_j$  is said to dominate block  $b_i$  if any path from a node in  $b_i$  to a primary output passes through a node in  $b_j$ .

Block b<sub>j</sub> is said to dominate block b<sub>i</sub> if any path from a node in b<sub>i</sub> to a primary output passes through a node in b<sub>j</sub>.

Theorem [Mangassarian, Veneris, Smith, Safarpour-ICCAD'11]:

If b<sub>j</sub> is a solution block, and b<sub>i</sub> dominates b<sub>j</sub>, then b<sub>i</sub> is also a solution block

Block  $b_j$  is said to dominate block  $b_i$  if any path from a node in  $b_i$  to a primary output passes through a node in  $b_j$ .

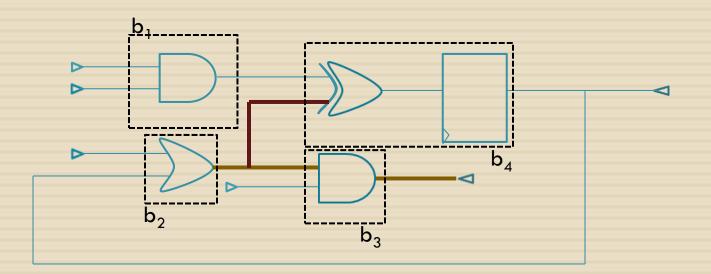

No block dominates b<sub>2</sub>

#### **Reverse Dominators**

□ A block  $b_i$  is a reverse dominator of block  $b_j$  if and only if  $b_i$  dominates  $b_i$ , denotes  $b_i D^{-1} b_i$ .

Block  $b_1$  is a reverse dominator of  $b_4$

#### Non-solution Implications

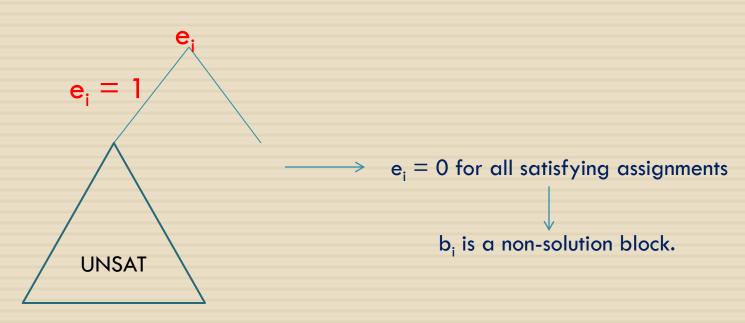

**Definition:** Block  $b_i$  is a non-solution block iff  $e_i = 0$  for all satisfying assignments.

#### Theorem:

If  $b_j$  is a non-solution block, and  $b_i D^{-1} b_j$ , then  $b_i$  is also a non-solution block

If  $b_4$  is a non-solution block,  $b_1$  is also a non-solution block. But how would we know that  $b_4$  is a non-solution in the first place?

| Introduction                                                  | <ul><li>SAT-based Design Debugging</li><li>Motivation and Previous Work</li></ul>                                                  |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Non-Solution<br>Implications                                  | <ul> <li>Dominators and Reverse Dominators</li> <li>Non-Solution Implications from Reverse<br/>Domination Relationships</li> </ul> |

| SAT Branching<br>Scheme for Early<br>Non-Solution<br>Learning | <ul><li>SAT Branching Scheme</li><li>Non-Solution Detection</li></ul>                                                              |

| Results and Final<br>Remarks                                  | • Experimental Results                                                                                                             |

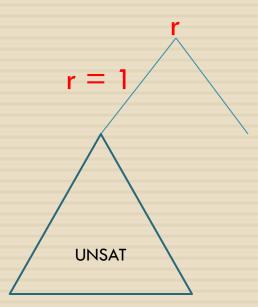

# **SAT Branching Scheme**

A decision tree in a SAT solver gives the order in which variables are decided upon. Consider the decision tree:

r = UNSAT

# **SAT Branching Scheme**

r =

UNSAT

A decision tree in a SAT solver gives the order in which variables are decided upon. Consider the decision tree:

$\rightarrow$  r = 0 for all satisfying assignment

# **SAT Branching Scheme**

UNSAT

A decision tree in a SAT solver gives the order in which variables are decided upon. Consider the decision tree:

r = 0 for all satisfying assignment

If after analyzing r = 1, SAT Solver returns no satisfying assignment and starts analyzing r = 0, clearly r = 0 for any satisfying assignment (if one exists).

What we have so far:

What about:

e

$e_{2} =$

UNSAT

e<sub>2</sub>

$e_i =$

UNSAT

$e_1 =$

UNSAT

In general, we can incrementally detect non-solution blocks. For example:

$\rightarrow$  ( $e_1 = 0$ ) for all satisfying assignment

$(e_2 = 0)$  for all satisfying assignment

$\rightarrow (e_i = 0)$  for all satisfying assignment

•  $e_2$ , ...  $e_i$  are also detected as non-solution blocks even though they are not the root of the decision tree.

e,

Deciding on the error-select variables first forces the SAT solver to learn about them faster

Pruning using non-solution implications can have a stronger effect

#### Algorithm Overview

Rearrange the order such that error select variables e appear first in the decision tree.

Extract learned non-solution blocks by inspecting the decision tree.

Use reverse domination relationships to learn more non-solution blocks. Add a blocking clause for each implied non-solution block.

| Introduction                                                  | <ul><li>SAT-based Design Debugging</li><li>Motivation and Previous Work</li></ul>                                                  |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Non-Solution<br>Implications                                  | <ul> <li>Dominators and Reverse Dominators</li> <li>Non-Solution Implications from Reverse<br/>Domination Relationships</li> </ul> |

| SAT Branching<br>Scheme for Early<br>Non-Solution<br>Learning | <ul><li>SAT Branching Scheme</li><li>Non-Solution Detection</li></ul>                                                              |

| Results and Final<br>Remarks                                  | • Experimental Results                                                                                                             |

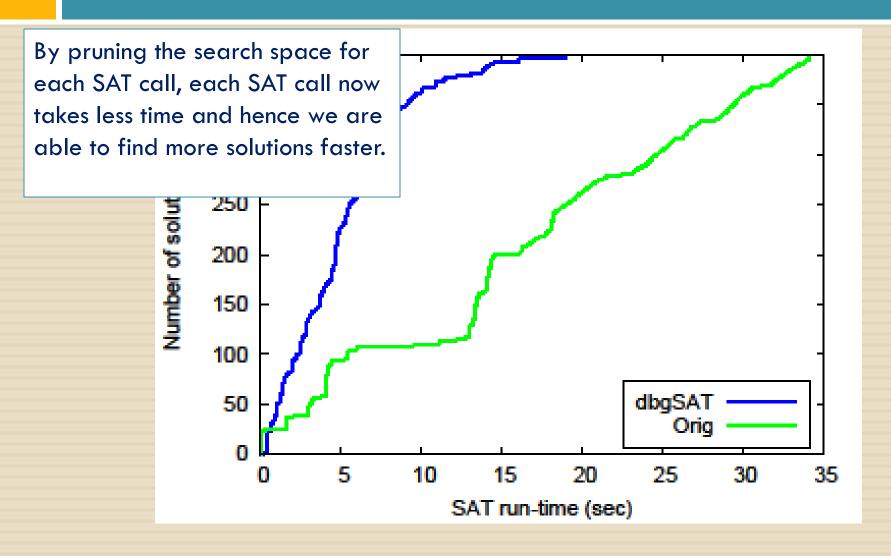

Platform: i5 3.1Ghz, 8GB memory, 2 hour time-limit.

- Benchmarks: Eight Opencores circuits and three industrial designs. For each, several bugs are injected to generate debugging instances.

- We modified MiniSAT 2.2.0 to implement our techniques.

MiniSAT vs. dbgSAT

We compare to a state-of-the-art SAT-based debugger with solution implications [Mangassarian, etal-ICCAD'11]:

| On average, 28% of non-      |            | MiniSAT(s) | Non-Sol(%) | dbgSAT(s) | lmp(x) |      |

|------------------------------|------------|------------|------------|-----------|--------|------|

| Solution blocks are implied  |            | T/O        | 74%        | 6955.90   | ∞      |      |

|                              | rsdecoder2 | 13564      | 33.35      | 58%       | 20.46  | 1.6x |

|                              | usb_funct1 | 35158      | 53.17      | 21%       | 45.46  | 1.2x |

| For rsdecoder, while MiniSAT |            | 134.46     | 32%        | 117.83    | 1.1x   |      |

| times out, we are able to    |            | 123.89     | 28%        | 97.26     | 1.3x   |      |

| solve it in under two hours. |            | 49.14      | 41%        | 36.90     | 1.3x   |      |

|                              | wb_dma3    | 299862     | 304.18     | 61%       | 182.09 | 1.7x |

|                              | vgal       | 89412      | 434.81     | 13%       | 172.51 | 2.5x |

| -                            | vaa2       | 89402      | 106.98     | 8.1%      | 147.95 | 0.7x |

| For certain cases, only      |            | 7.97       | 0%         | 3.94      | - 2.0x |      |

| rearranging the order of     |            | 12.53      | 17%        | 24.67     | 0.5x   |      |

| variables improves the       |            | 11.76      | 0%         | 4.78      | 2.5x   |      |

| performance                  |            | 22.08      | 6%         | 13.51     | 1.6x   |      |

|                              | Instance     | # of Nodes | MiniSAT | Non-Sol(%) | dbgSAT | lmp(x) |

|------------------------------|--------------|------------|---------|------------|--------|--------|

| 23/25 cases show improvement |              | 48.45      | 44%     | 33.42      | 1.4x   |        |

| 20/200                       | open_sparcz  | 04910      | 44.11   | 50%        | 39.39  | 1.1x   |

|                              | Design 1 - 1 | 499325     | 53.40   | 0.1%       | 25.08  | 2.1 x  |

|                              | Design1-2    | 499705     | 72.54   | 25%        | 38.27  | 1.9x   |

|                              | Design1-3    | 499696     | 39.63   | 1%         | 31.69  | 1.3x   |

|                              | Design1-4    | 499705     | 100.89  | 29%        | 45.69  | 2.2x   |

|                              | Design1-5    | 499705     | 73.72   | 29%        | 27.04  | 2.7x   |

|                              | Design2-1    | 45632      | 18.47   | 10%        | 14.59  | 1.3x   |

|                              | Design2-2    | 203706     | 7.38    | 0.7%       | 4.23   | 1.7x   |

|                              | Design2-3    | 2082       | 0.13    | 53%        | 0.08   | 1.6x   |

|                              | Design3-1    | 5454       | 3.03    | 51%        | 2.07   | 1.6x   |

|                              | Design3-2    | 2333       | 0.083   | 44%        | 0.07   | 1.2x   |

|                              | Average      |            |         |            |        | 1.68x  |

#### Conclusions

#### Summary

Non-solution implications using reverse domination to prune the search space of design debugging SAT calls.

A SAT branching scheme to detect non-solution early and enhance non-solution implications.

Future Work

Study the error-select variables' order to maximize the implications (solution + non-solution).

Extend the work to higher cardinality.

# Questions/Discussions